# Specification GAYLE Gate array for A300/A500+

ALS<u>O IN</u> A1200

#### 1 .O DESCRIPTION

GAYLE is a gate array IC used in the A'300 and related systems. It is packaged in an 84 pin plastic leaded chip carrier (PLCC) whose pinout is shown below. GAYLE is capable of operating a 68000 based Amiga computer with the ECS chipset, and a processor clock speed of 7.16 Mhz. GAYLE provides the following functions:

- Address decoding and timing for system ROM

- Address decoding and timing for optional flash ROM

- Address decoding and timing for chip RAM

- Address decoding and timing for chip registers

- Address decoding and timing for 8520's (CIA's)

- Address decoding and timing for real time clock (RTC)

- Address decoding and timing for Credit card connector

- Address decoding and timing for IDE hard disk drive

- Address decoding and timing for COM200020 ArcNet chip

- Generation of ECLK clock signal

- Data buffer control

- System RESET logic

- Floppy glue

{ Insert pinout here }

#### 1.1 CONFIGURATION

The device shall be configured as a standard 84 pin plastic leaded chip carrier with external dimensions as shown in Figure XX-x. Refer to figure x-x for connection diagram.

1.2 SOURCES Refer to Approved Vendor List.

## **1.3 PIN DESCRIPTIONS**

| NUM      | <u>CLASS</u> | NAME               | DESCRIPTION                                                      |

|----------|--------------|--------------------|------------------------------------------------------------------|

| 1        | OUT          | PE12               | Program Voltage 12V Enable                                       |

| 2        | OUT          | PE5                | Program Voltage 5V Enable                                        |

| 3        | PWR          | Gndl               | Ground                                                           |

| 4        | TS           | NOISE              | Digital Audio                                                    |

| 5        | OUT          | CC-RESET           | Memory Card Reset                                                |

| 6<br>7   | OUT<br>OUT   | _CC_ENA<br>_CC_REG | Memory Card Enable                                               |

| 8        | OUT          | _CC_CEL            | Memory Card "Register" Space<br>Memory Card Chip Enable Low byte |

| 9        | OUT          | _CC_CEU            | Memory Card Chip Enable High byte                                |

| 10       | OUT          | Ē                  | CIA Phi 2                                                        |

| 11       | OUT          | FLASH              | Flash Memory Chip Enable                                         |

| 12       | IN           | _IDE_IRQ           | IDE Drive Interrupt Request                                      |

| 13       | OUT          | $\_IDE\_CS(1)$     | IDE Drive Chip Select 1                                          |

| 14       | OUT          | $\_IDE\_CS(2)$     | IDE Drive Chip Select 2                                          |

| 15       | OUT          | -SPARE-CS          | Spare Chip Select                                                |

| 16<br>17 | OUT<br>OUT   | _NET_CS<br>_RTC_CS | Network Controller Chip Select                                   |

| 17       | OUT          | IOWR               | Real Time Clock Chip Select<br>I/O Write Strobe                  |

| 10       | OUT          | IORD               | I/O Read Strobe                                                  |

| 20       | PWR          | vcc 1              | +5V                                                              |

| 21       | OUT          | _ROMEN             | ROM Chip Enable                                                  |

| 22       | IN           | C14M               | 14 MHz Člock In (master)                                         |

| 23       | IN           | CCK                | CCK Clock IN (sync)                                              |

| 24       | PWR          | Gnd2               | Ground                                                           |

| 25<br>26 | IN<br>IN     | XRDY<br>_OVR       | Expansion Bus Wait                                               |

| 20<br>27 | OC           | OEL                | Expansion Bus Decode Override<br>Chip->68000 Bus Buffer Enable   |

| 28       | 0 C          | OEB                | 68000->Chip Bus Buffer Enable                                    |

| 29       | IN           | DBR                | Agnus Chip Data Bus Required                                     |

| 30       | OUT          | BLS                | Agnus Chip Blitter Slowdown                                      |

| 31       | OUT          | _REGEN             | Agnus Chip Register Enable                                       |

| 32       | OUT          | _RAMEN             | Agnus Chip RAM Enable                                            |

| 33       | IN<br>IN     | _AS                | 68000 Address Strobe                                             |

| 34<br>35 | IN<br>IN     | _UDS<br>_LDS       | 68000 Upper Data Strobe<br>68000 Lower Data Strobe               |

| 36       | IN           | R_W                | 68000 Read/Write                                                 |

| 37       | TS           | _DTACK             | 68000 Data Transfer Acknowledge                                  |

| 38       | IN           | _BGACK             | 68000 Bus Grand Acknowledge                                      |

| 39       | o c          | _HLT               | 68000 Halt                                                       |

| 40       | 0 C          | _RST               | 68000 Reset                                                      |

| 41       | IN           | A12                | 68000 Address Bit 12                                             |

| 42       | IN<br>IN     | A13                | 68000 Address Bit 13                                             |

| 43<br>44 | IN<br>IN     | A14<br>A15         | 68000 Address Bit 14<br>68000 Address Bit 15                     |

| 44       | PWR          | Gnd3               | Ground                                                           |

| 46       | IN           | A16                | 68000 Address Bit 16                                             |

| 47       | IN           | A17                | 68000 Address Bit 17                                             |

| 48       | IN           | A18                | 68000 Address Bit 18                                             |

| 49       | IN           | A19                | 68000 Address Bit 19                                             |

| 50       | IN           | A20                | 68000 Address Bit 20                                             |

GAYLE Specification

| 51<br>52<br>53<br>54<br>55<br>56<br>57<br>58<br>59<br>60<br>61<br>62<br>63<br>64<br>65<br>66<br>67<br>68<br>69<br>70<br>71<br>72<br>73<br>74<br>75<br>76<br>77<br>78<br>79<br>80<br>81<br>82 | IN<br>IN<br>IN<br>IO<br>IO<br>IO<br>IO<br>IO<br>IO<br>IO<br>IO<br>IO<br>IO<br>IO<br>IO<br>IO | A21<br>A22<br>A23<br>D7<br>D6<br>D5<br>D4<br>D3<br>D2<br>D1<br>D0<br>vcc2<br>_KBRESET<br>DKWEB<br>DKWDB<br>Gnd4<br>MTRON<br>MTRX<br>D K W E<br>_DKWD<br>_MTR<br>_SEL<br>-ODD-CIA<br>-EVEN-CIA<br>_CC_CD(1)<br>_CC_CD(2)<br>_CC_BVD(1)<br>_CC_BVD(2)<br>CC_WP<br>_CC_BUSY_IREQ<br>-WAIT<br>_BERR | 68000 Address Bit 21<br>68000 Address Bit 22<br>68000 Data Bit 7<br>68000 Data Bit 7<br>68000 Data Bit 5<br>68000 Data Bit 5<br>68000 Data Bit 3<br>68000 Data Bit 2<br>68000 Data Bit 2<br>68000 Data Bit 1<br>68000 Data Bit 0<br>+5V<br>Keyboard Reset In<br>Floppy Write Enable Out<br>Floppy Write Data Out<br>Ground<br>Floppy Motor On Out<br>Floppy Write Enable In<br>Floppy Write Data In<br>Floppy Write Data In<br>Floppy Write Data In<br>Floppy Write Data In<br>Floppy Select In<br>CIA Odd Chip Select<br>CIA Even Chip Select<br>Memory Card Card Detect 1<br>Memory Card Battery Voltage Detect 1<br>Memory Card Battery Voltage Detect 2<br>Memory Card Battery Voltage Detect 3<br>Memory Card Write Protect<br>Memory Card Busy/Interrupt Request<br>Memory Card Wait<br>Bus Error Interrupt Request |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                              |                                                                                              | -WAIT                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 82                                                                                                                                                                                           |                                                                                              |                                                                                                                                                                                                                                                                                                 | Bus Error Interrupt Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 83                                                                                                                                                                                           | 0 C                                                                                          | _INT6                                                                                                                                                                                                                                                                                           | High Priority Interrupt Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 84                                                                                                                                                                                           | 0 C                                                                                          | _INT2                                                                                                                                                                                                                                                                                           | Low Priority Interrupt Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                              |                                                                                              |                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

.....

. . ...

.....

- - --

### 2.0 SYSTEM ROM

The onboard ROMs are selected in the address range from \$0A80000 to \$0B7FFFF, \$0E00000 to \$0E7FFFF, and \$0F80000 to \$0FFFFFF. The ROMs are also selected in the range from \$00000000 to \$01FFFFF when the internal overlay signal (OVL) is high (this allows the RESET vectors to be contained in the ROMs). The internal OVL signal becomes asserted at reset, and negates on the first write to CIA1 (address range of \$BFD000 to \$BFDFFF.

. ....

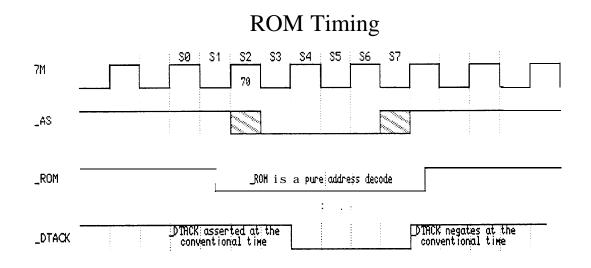

### 2.1 ROM Timing

ROM timing is shown below:

#### 3.0 FLASH ROM

There is provision for an optional flash ROM device. The intent is that this is a possible replacement for a floppy disk drive in an extremely low end variant of the A300. The enable for the flash rom is called -FLASH-CE, and is active in the address range from \$OAOOOOO to \$0A7FFFF. This output is enabled when the proper data strobe is asserted, and the address is in range. Generation of \_DTACK is identical to that for system ROM accesses.

#### 3.0 CHIP RAM

Chip RAM cycles are generated during accesses to locations \$0000000 to \$0200000. When the internal OVL signal is asserted, ROM appears in this space instead of chip RAM (see section on ROM for further information on OVL).

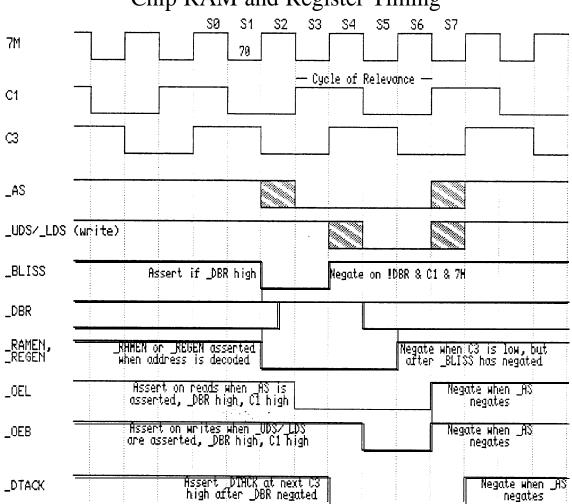

#### 3.1 Chip RAM Timing

Timing for chip RAM cycles is given in the timing section of the Chip Register discussion (section 4.1). All timings given are equally valid for either chip registers or chip RAM.

### 4.0 CHIP REGISTERS

The chip registers are selected in the range from \$0DFF000 to \$0DFF1FF. Chip registers show up in user and supervisor data space.

4.1 Chip RAM and Register Timing

Timing is given on the following page. Note that timimng for chip RAM accesses is identical. A wait state is inserted when the access is from a DMA device.

# Chip RAM and Register Timing

## 5.0 CIA'

The 8520 CIA's are selected in the address range from \$0BF0000 to \$0BFFFFF. ODD-CIA responds to addresses in this range in which address line 12 is low, with data appearing at odd addresses. The standard location to use in accessing ODD-CIA is from \$0BFE000 to \$0BFEFFF. EVEN-CIA responds to addresses from \$0BF0000 to \$0BFFFFF in which address line 13 is low, with data appearing at even addresses. The standard location to use for accessing this CIA is from \$0BFD000 to \$0BFDFFF.

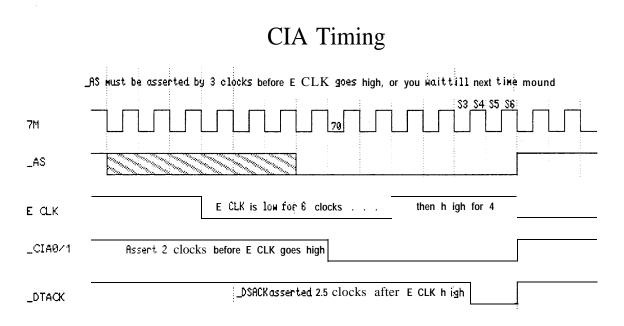

#### 5.1 CIA timing

GAYLE provides synchronization of the processor to CIA accesses as well as generation of the E clock signal. Timing is shown below:

#### 6.0 REAL-TIME CLOCK

The real-time clock (RTC) is selected in the address range from \$ODCOOOO to \$ODCFFF. The RTC appears in both user and supervisor spaces.

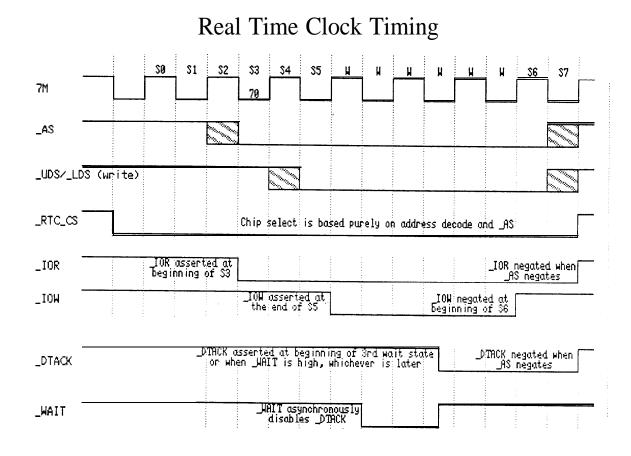

## 6.1 RTC Timing

The real-time clock timing is based on the Ricoh RP5C01 real-time clock chip. GAYLE's timing to the RTC is shown below:

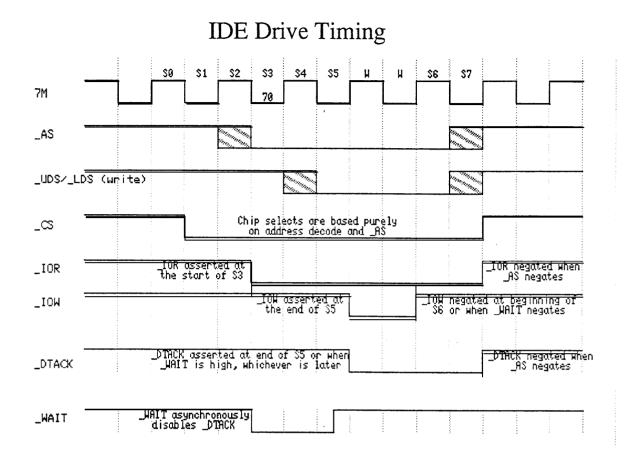

#### 7.0 IDE HARD DRIVE

The IDE (AT) hard drive requires two mutually exclusive chip selects. Please see the chart below for address range in which each is active. The \_IOW and \_IOR signals have timing that is valid for IDE hard drives during these cycles.

Data register accesses can be performed faster than control register accesses. Accesses to the control registers are called "8 bit accesses" while those to the data register are called "16 bit accesses". Show: oelow is a table that gives the chip select and access speed versus address range.

| <u>A1-1</u> | <u>A13</u> | <u>A12</u> | Address Range          | Chip Select | Speed  |

|-------------|------------|------------|------------------------|-------------|--------|

| Ű           | 0          | 0          | \$0DA0000 to \$0DA0FFF | CS 1        | 8 bit  |

| 0           | 0          | 1          | \$0DAl000 to \$0DA1FFF | CS2         | 8 bit  |

| 0           | 1          | 0          | \$0DA2000 to \$0DA2FFF | CS 1        | 16 bit |

| 0           | 1          | 1          | \$0DA3000 to \$0DA3FFF | CS2         | 16 bit |

| 1           | 0          | Х          | \$0DA4000 to \$0DA5FFF | None        | 8 bit  |

| 1           | 1          | Х          | \$0DA6000 to \$0DA7FFF | None        | 16 bit |

## 7.1 IDE Timing

IDE timing is shown below:

.....

#### 7.3 IDE Register Map

The disk drive address lines DAO, DA1, and DA2 are expected to be connected to processor address lines A2, A3, and A4 respectively. When connected in this fashion, the following memory map results:

| <u>Addr on A 1000+</u> | Addr on AT | Valid Data | Read Function    | Write Function  |

|------------------------|------------|------------|------------------|-----------------|

| \$0DA0018              | 3F6        | 8 bits     | Alternate Status | 'Device Control |

| \$0DA001C              | 3F7        | 8 bits     | Drive address    | Not used        |

| \$0DA1004              | 1F1        | 8 bits     | Error Register   | Features        |

| \$0DA1008              | 1F2        | 8 bits     | Sector Count     | Sector Count    |

| \$0DA100C              | 1F3        | 8 bits     | Sector Number    | Sector Number   |

| \$0DA1010              | 1F4        | 8 bits     | Cylinder Low     | Cylinder Low    |

| \$0DA1014              | 1F5        | 8 bits     | Cylinder High    | Cylinder High   |

| \$0DA1018              | 1F6        | 8 bits     | Drive/Head       | Drive/Head      |

| \$0DA101C              | 1F7        | 8 bits     | Status           | Command         |

| \$0DA2000              | 1F0        | 16 bits    | Data             | Data            |

## 8.0 ARCNET

A chip select is provided for an SMC COM20020 ARCNET chip. The COM20020 interfaces directly to the processor for all other signals.

## 8.1 ArcNet Timing

Timing for the SMC COM20020 is shown below:

# ArcNet Timing

{Insert timing diagram here}

#### 10.0 SYSTEM RESET LOGIC

The \_KBRESET input drives the open collector outputs RESET and -HALT low. No matter how short the pulse, GAYLE stretches the RESET and -HALT outputs to at least 560ns. When \_RESETis driven low (either by GAYLE or externally), all internal states in GAYLE are reset, including the registers, which are all set to '0'.

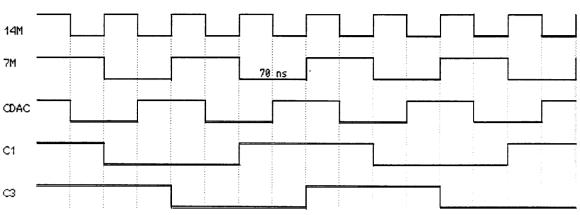

#### 11.0 SYSTEM CLOCKS

The system clocks expected by ANIMAL are shown below. Note that C3 is generated internally.

### 12.0 FLOPPY GLUE

The floppy signals MTRON, MTRX, DKWDB, and DKWEB are generated by GAYLE. All of these signals are open collector outputs.

MTRON is the signal that tells the floppy motor to turn on. It is the \_MTR input latched by the \_SEL input. MTRON is guaranteed negated when RESET is asserted.

MTRX is the signal that tells the floppy motor to do what, George? It follows the \_ MTR input except during reset when it is guaranteed negated.

DKWDB is a buffered version of the \_DKWD signal.

DKWEB follows DKWE, except it is negated during reset.

#### 13.0 BUFFER CONTROL

SHould this be folded in with other sections, or is there something special to say, George?

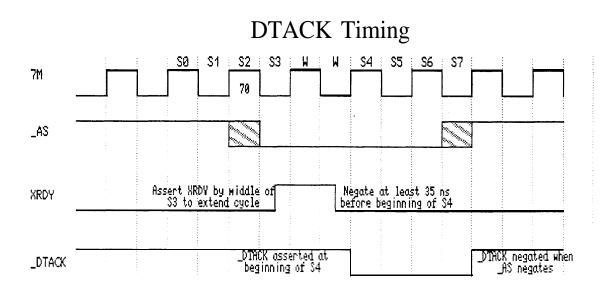

#### 14.0 DTACK GENERATION

Automatic generation of the 68000 cycle termination signal, DTACK, is provided. GAYLE decodes addresses to determine timing for the DTACK signal. Timing for DTACK is given in many of the individual sections of this specification, but for any address ranges not covered in other sections (such as expansion space), DTACK works as follows:

1. If \_OVR or XRDY are not asserted, DTACK is generated at the beginning of S4, guaranteeing a 4 clock cycle.

2. When \_OVR is asserted, the \_DTACK output is tristated, allowing the device that asserted \_OVR to generate its own \_DTACK.

3. If XRDY is asserted in time, generation of \_DTACK is held off until XRDY is negated.

#### 14.1 DTACK Timing

Timing for DTACK is shown below:

#### 15.0 OVR AND XRDY SIGNALS

In addition to its function in overriding the generation of \_DTACK, the \_OVR signal can override address decoding in GAYLE. Thus it can be used to allow external devices to reside in address ranges that are normally reserved for motherboard devices, such as the credit card interface. Use of \_OVR for this use basically requires that \_OVR is asserted earlier than \_AS. Address ranges where this is effective are shown below:

| Address range       | Normal_cvcle_tvpe      | Cycle type with OVR |

|---------------------|------------------------|---------------------|

| \$A00000 -\$A7FFFF  | Flash ROM              | zorro II            |

| \$A80000 -\$B7FFFF  | Workbench ROM          | zorro II            |

| \$B80000 -\$BEFFFF  | Reserved for CDTV      | Zorro II            |

| \$DB0000-\$DB0000   | External IDE drive     | Zorro II            |

| \$DD0000-\$DDFFFF   | Reserved for DMA contr | ZOITO II            |

| \$EOOOOO - \$E7FFFF | System ROM             | zorro II            |

| \$F80000 -\$FFFFFF  | System ROM .           | zorro II            |

Any address ranges where \_OVR is legal, use of the XRDY signal to extend the cycle is also legal. Other address ranges ignore the XRDY signal.

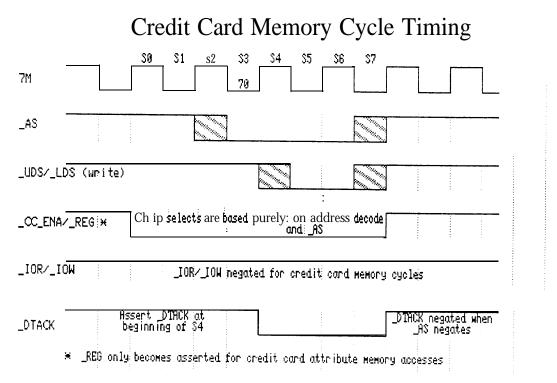

#### 16.0 CREDIT CARD INTERFACE

GAYLE includes a complete interface to the industry standard PCMCIA cartridge. Limited support of hot insertion and removal is included. GAYLE supports three different kinds of credit card cycles:

- Credit card memory cycles

- Credit card attribute memory cycles

- Credit card I/O cycles

#### 16.1 Credit card memory cycles

These cycles are active during accesses of address \$4000'00 to \$8FFFFF while a credit card is inserted. Accesses from \$400000 to \$7FFFFF are to the credit card main memory. Accesses from \$8000000 to \$8FFFFF are to credit card attribute memory. Both types of cycles are identical, except credit card attribute cycles assert \_CC\_REG and \_CC\_ENA, while main memory cycles just assert \_CC\_ENA. This represents 4 MB of directly accessable main memory address space. The full 64MB of defined address space may be reached using the page registers in GAYLE. Currently GAYLE does not actually support these, but future versions may very well do so.

16.2 Credit card memory cycle timing

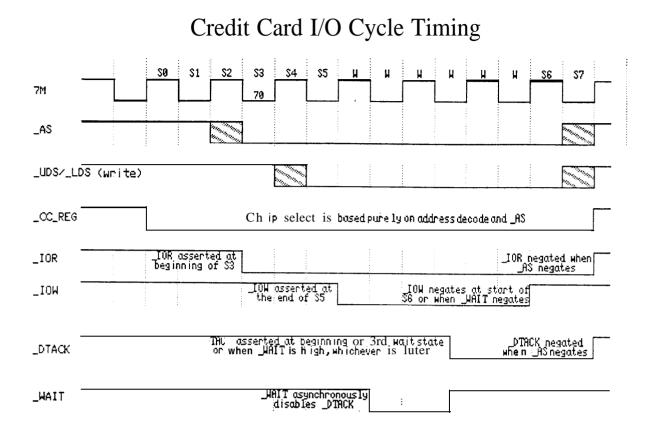

#### 16.3 Credit card I/O cycles

Credit card I/O cycles occur during accesses to \$900000 to \$9FFFFF while a credit card is inserted.

#### 16.4 Credit card I/O timing

Timing for credit card I/O cycles is shown below:

## 17.0 Test Mode

If \_OVR is asserted at the rising edge of \_KBRESET, a test mode is entered in which the E clock state counters reset to a known condition.

#### 18.0 SPARE chip select

A spare chip select is provided. It is asserted on any access to locations \$D80000 to \$D8FFFFF. Timing is similar to the ARCNET chip select.

#### 19.0 GAYLE Registers

Four registers are included that facilitate support of the cartridge slot and IDE interrupt management. All registers are set to zero at reset time. These registers are shown on the following two pages:

Address **\$DA8000**

| <u>Bit 15</u> | Rit 14        | Bit 17  | Rit 17  | Rit 11    | Rit 10  | Rit 9   | Rit 8   |

|---------------|---------------|---------|---------|-----------|---------|---------|---------|

| IDE int       | CC det status | BVD2/DA | BVD1/SC | WR enable | BSY/IRQ | Dig Aud | c c     |

| status        |               | status  | status  | status    | status  | enable  | disable |

- Bit 8: Allows the software to disable the credit card interface altogether. Writing a value of '1' disables the credit card interface, '0' allows it to become enabled (having no credit card installed also disables the interface. Disabling the credit card interface includes disabling address decoding for the credit card areas, makes the credit card inputs appear to be in the inactive state, and inhibits status change interrupts.

- Bit 9: Enable for the credit card digital audio output. Writing a '1' enables connecting the credit card digital audio to the amiga audio and disables the BVD2 input to the interrupt request logic.

- Bits 10-15: Each represent an external line. Reading any of these allows the software to determine the current state of the specified line. Writing a value of 1 to any of these bits allows the software to force GAYLE to behave as if the specified line is asserted (including returning a '1' when this register is read). If the credit card is not inserted, or if the CC disable bit is asserted, the credit card lines will

all appear to be negated, although any lines that the software has written a '1' to will still read back as a '1'. The external lines are as follows:

| IDE int   | Interrupt output of the IDE drive; this bit is high whenever the IDE drive is         |

|-----------|---------------------------------------------------------------------------------------|

| CC dat    | generating an interrupt                                                               |

| CC det    | Credit card detect: this bit is high whenever a credit card is present                |

| BVD2/DA   | Battery voltage detect 2 / Digital audio                                              |

| BVD1/SC   | Battery voltage detect 1 / Credit card (internal) status change                       |

| WR enable | Write enable; this bit is high when the credit card is write enabled. When low writes |

|           | are inhibited.                                                                        |

| BSY/IRQ   | Credit card busy/Interrupt request                                                    |

Address SDA9000

| Bit 15         | Rit 14        | Rit 13            | Rit 12            | Bit 11            | Rit 10            | Rit 9                        | Rit 8                            |

|----------------|---------------|-------------------|-------------------|-------------------|-------------------|------------------------------|----------------------------------|

| IDE int change | CC det change | BVD2/DA<br>change | BVD1/SC<br>change | WR prot<br>change | BSY/IRQ<br>change | Reset on CC<br>status change | Berr on access after stat change |

Bit 8: Allows the software to tell GAYLE to generate a reset whenever the credit card detect status line has changed (i.e. the credit card has been inserted/removed).

Bit 9: Causes a bus error to be generated on any access to the credit card area after the credit card detect status line has changed.

Bits 10-15: Are the same signals as at address SDA8000, but the register at SDAAOOO tells you when any of these bits has changed value. The bit remains high (and the interrupt line remains active) until a '0' is written to that bit. Writing a '1' will cause a bit to be unchanged.

#### Address **\$DAA000**

| Bit 15                 | Bit 14                                                                                                       | Rit 13                                                                                                                                                          | Rit 13                | Rit 11                 | Rit 10                | Rit 9                  | Rit 8             |

|------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------|-----------------------|------------------------|-------------------|

| IDE int<br>int2 enable | CC det<br>int6 enable                                                                                        | BVD2/DA<br>int enable                                                                                                                                           | BVD1/SC<br>int enable | WRenable<br>in2 enable | BSY/IRQ<br>int enable | BVD/DA/SC<br>int level | BSY/IRQ int level |

| Bit 8:                 |                                                                                                              | Sets the interrupt level that is generated when the BSY/IRQ (bit 10) status line changes state, a '1' indicates in6t should be generated, a '0' indicates int2, |                       |                        |                       |                        |                   |

| Bit 9:                 | Similar to bit                                                                                               | 8, except it is                                                                                                                                                 | for the BVD (         | bits 12 and 13)        | inputs.               |                        |                   |

| Bit 10:                |                                                                                                              | Enables interrupt on status change of the BSY/IRQ line of the credit card interface. The interrupt level that is generated is programmed by bit 8.              |                       |                        |                       |                        |                   |

| Bit 11:                | Enables gene                                                                                                 | Enables generation of an int2 on status change of the write enable line of the credit card interface.                                                           |                       |                        |                       |                        |                   |

| Bit 12:                |                                                                                                              | Enables interrupt on status change of the BVDI/SC line of the credit card interface. The interrupt level that is generated is programmed by bit 9.              |                       |                        |                       |                        |                   |

| Bit 13:                |                                                                                                              | Enables interrupt on status change of the BVD2/DA line of the credit card interface. The interrupt level that is generated is programmed by bit 9.              |                       |                        |                       |                        |                   |

| Bit 14:                | Enables generation of an int6 on status change of the credit card detect lines of the credit card interface. |                                                                                                                                                                 |                       |                        |                       |                        |                   |

| Bit 15:                | Enables gene                                                                                                 | ration of an in                                                                                                                                                 | t3 on status ch       | ange of the int        | errupt line of t      | he IDE interfac        | ce.               |

- -----

مسر یا

#### Address \$DAB000

| Bit 15      | Rit 14      | Rit 13      | Rit 12      | Bit 11   | Rit 10      | Rit 9       | Rit 8      |

|-------------|-------------|-------------|-------------|----------|-------------|-------------|------------|

| Page reg 25 | Page reg 24 | Page reg 23 | Page reg 22 | Slow mem | Delay write | Program 12v | Program 5V |

- Bit 8: Enables the programmable 5 volt output. Setting both bit 8 and bit 9 together asserts the credit card reset signal. Note: Credit card not inserted or disabled forces the programmable 5 volt output to zero.

- Bit 9: Enables the programmable 12 volt output. Setting both bit 8 and bit 9 together asserts the credit card reset signal. Note: Credit card not inserted or disabled forces the programmable 12 volt output to zero.

- Bit 10: Enables a mode where the credit card WAIT signal is looked at during writes (it is always looked at during reads). In a 68000 this necessitates insterting a wait state. When set to zero, zero wait state cycles are run.

- Bit 11: Enables 1.2 us memory cycles (instead of the normal 560ns).

- Bits 12 -15: Are for the currently unimplemented credit card page registers. You can tell they are unimplemented because they do not read back what is written.

## 17.0 MEMORY MAP

.....

.

| 0000000 to 01FFFFF | 2MB    | Chip RAM (or system ROM in overlay)                  |

|--------------------|--------|------------------------------------------------------|

| 0200000 to 03FFFFF | 2MB    | Zorro II expansion space                             |

| 0400000 to 07FFFFF | 4MB    | Credit Card memory if CC present (ZII otherwise)     |

| 0800000 to 08FFFFF | 1MB    | Credit Card attributes if CC present (ZII otherwise) |

| 0900000 to 09FFFFF | 1MB    | Credit Card I/O if CC present (ZII otherwise)        |

| OAOOOOO to 0A7FFFF | 512 KB | Flash ROM                                            |

| OA80000 to 0B7FFFF | 1 MB   | System ROM selected (optional workbench ROM)         |

| 0B80000 to OBEFFFF | 448 KB | Not used (Reserved for CDTV)                         |

| OBFOOOO to OBFFFFF | 64 KB  | CIA's (See section on CIA's for more detail)         |

| OCOOOOO to 0D7FFFF | 1.5 MB | COO000 Memory                                        |

| OD80000 to 0D8FFFF | 64 KB  | SPARE chip select                                    |

| OD90000 to 0D9FFFF | 64 KB  | ARCNET chip select                                   |

| ODAOOOO to 0DA3FFF | 16KB   | IDE drive (see section on IDE for register map)      |

| 0DA4000to 0DA4FFFF | 16 KB  | IDE reserved                                         |

| 0DA8000to ODAFFFF  | 32 KB  | Credit Card & IDE configuration registers            |

| 0DB0000 to ODBFFFF | 64 KB  | Not used (Reserved for external IDE)                 |

| ODCOOOO to ODCFFFF | 64 KB  | Real time clock                                      |

| ODD0000 to ODDFFFF | 64 KB  | RESERVED for DMA controller                          |

| ODE0000 to ODEFFFF | 64 KB  | Not Used                                             |

| ODFOOOO to ODFFFFF | 64 KB  | Chip registers (shadowed 8 times)                    |

| OE00000 to 0E7FFFF | 512 KB | System ROM (1st half if 1MB ROM)                     |

| OE80000 to OEFFFFF | 512 KB | Configuration and I/O card space                     |

| OF00000 to 0F7FFFF | 512 KB | Cartridge space                                      |

| OF80000 to OFFFFFF | 512 KB | System ROM (2nd half if 1MB ROM)                     |

|                    |        |                                                      |

## 18.0 PHYSICAL REQUIREMENTS

18.1 Marking

Devices shall be marked with Commodore part number plus a copyright notice as follows: 1990 CBM.

18.2 Packaging

The interconnected circuitry shall be contained in a standard 84-pin plastic leaded chip carrier with exterminal dimensions shown in Figure XX-X.

#### 19.0 PROCESS QUALIFICATION TESTS

Integrated circuitrs supplied to the requirements of this specification shall meet the requirements of Engineering Policy No. 1.02.008, whatever that is. Supporting doucmentation shall be supplied by vendor upon request.

19.1 Environmental test conditions

Devices shall comply with blah blah