Kategorien

Kategorien

Dies ist eine alte Version des Dokuments!

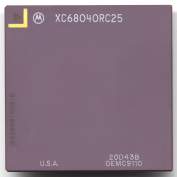

Der Motorola 68040 ist ein 32-Bit-Mikroprozessor des Unternehmens Motorola. Er verfügt in der vollen Version über zwei integrierte MMUs (gemäß der Harvard-Architektur) und eine dem Motorola 68881/68882 fast vollständig kompatible FPU, sowie einem Level-1-Cache von 4 KB für jeweils Daten und Instruktionen. Damit leistet er im Integer-Bereich etwa doppelt so viel wie ein gleich getakteter Motorola 68030. Die integrierte FPU ist mehr als doppelt so effizient wie ein Motorola 68882. Sie folgt dabei dem IEEE 754 Floating Point Standard und beinhaltet keine Logik für trigonometrische Funktionen, diese müssen in Software nachgebildet werden.

http://www.freescale.com/webapp/sps/site/prod_summary.jsp?code=MC68040

http://www.freescale.com/webapp/sps/site/prod_summary.jsp?code=MC68040

The MC68040, MC68040V, MC68LC040, and MC68EC040 are Freescale Semiconductor's (formerly Motorola, Inc., Semiconductor Products Sector) fourth generation of M68000-compatible, high-performance, 32-bit microprocessors. All four devices are virtual memory microprocessors employing multiple concurrent execution units and a highly integrated architecture that provides very high performance. They integrate an MC68030-compatible integer unit (IU) and two independent caches. The MC68040, MC68040V, and MC68LC040 contain dual, independent, demand-paged memory management units (MMUs) for instruction and data stream accesses and independent, 4-Kbyte instruction and data caches. The MC68040 contains an MC68881/MC68882-compatible floating-point unit (FPU). The use of multiple independent execution pipelines, multiple internal buses, and a full internal Harvard architecture, including separate physical caches for both instruction and data accesses, achieves a high degree of instruction execution parallelism on all three processors. The on-chip bus snoop logic, which directly supports cache coherency in multimaster applications, enhances cache functionality. Features